PX5 NET with its native BSD sockets API has been certified by SGS-TÜV SAAR to the highest levels of the IEC 61508, IEC 62304, ISO 26262, and EN 50128 functional safety standards; it offers developers a faster path to certification, reduces product liability with improved quality and time to market.

The latest PX5 RTOS 5.3.0 release — first introduced in September 2025 — has enhanced performance and new functionality. The new functionality includes thread-local storage, event chaining, even-flag consumption options, time-slice modification, and system object information. It is also roughly 5-8% faster, making the fastest RTOS even faster (get even more performance with IAR compilation). Finally, this release is even more MISRA compliant, meeting 301 of the 306 MISRA C:2012 rules and directives analyzed by the advanced IAR C-STAT static analysis tool.

Click here for more info on how you can benefit from the best RTOS

Please check out the PX5 AI Assistant, powered by ChatGPT. It is knowledgeable about all of our products and where to find information and resources on our website. Of course, if you can’t get the information from the PX5 AI Assistant, please contact us!

Each thread requires RAM for its control block and stack. In addition, each thread requires processing cycles for its execution (context switching). Event notification APIs can be leveraged such that a thread can effectively suspend on multiple system objects thereby reducing the number of threads and extra resources they consume.

An important subset of C++17 multithreading support is now available with PX5 RTOS, enabling C++ developers to rely less on standard C code. The PX5 RTOS C++ support includes thread, mutex, condition variable, and semaphore classes. This support is development-tool-agnostic and can therefore be used with any embedded C++ compiler.

Please Contact Us for More Information

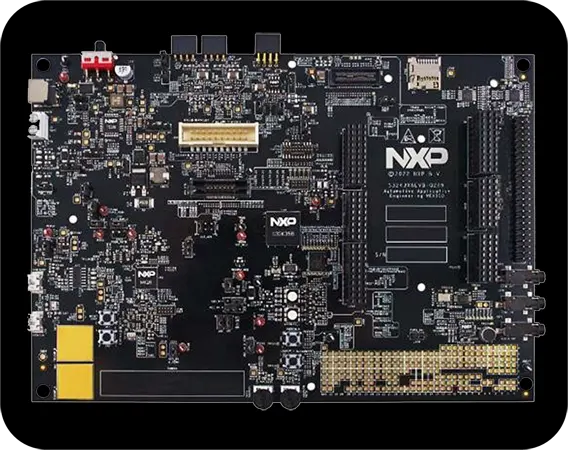

A free evaluation of PX5 RTOS for the S32K388EVB-Q289 (Cortex-M7) is available for evaluation. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS-specific extensions. It also includes a TCP Echo Server example using PX5 NET and the RTD Ethernet driver, PX5 FILE RAM Disk example, and a PX5 MODULES example with memory protection. This evaluation is based on S32 Design Studio development tools using the on-board JTAG debugger (other debug probes may be used).

PX5 RTOS now supports the Infineon TriCore architecture (TC3xx) in Asymmetric Multiprocessing (AMP) mode using the AURIX Development Studio (Tasking compiler). A full source code evaluation is available for the AURIX TC397 TFT EVAL board from Infineon using the on-board debug connection over USB.

PX5 RTOS now supports the AMD MicroBlaze soft core processor using the Vitis development tools (GCC compiler). A full source code evaluation is available for the ALINX AXKU040 board using the USB debug cable.

PX5 RTOS now supports the ST Stellar SR6GX (Cortex-R52) automotive integration MCU. An evaluation is available on the SR6G7-EVBC6000P evaluation board using the GCC compiler and the Lauterbach debugger.

A free evaluation of PX5 RTOS for the PIC32CK GC01 (Cortex-M33) is available for download on our website. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS specific extensions. This evaluation is based on MPLAB X IDE (GCC) using the on-board debugger.

A free evaluation of PX5 RTOS for the PIC32CM GC00 (Cortex-M0) is available for download on our website. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS specific extensions. This evaluation is based on MPLAB X IDE (GCC) using the on-board debugger.

A free evaluation of PX5 RTOS for the PIC32CZ CA80 (Cortex-M7) is available for download on our website. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS specific extensions. This evaluation is based on MPLAB X IDE (GCC) using the on-board debugger.

TinyUSB is a free, open-source USB host and device library integrated with the PX5 RTOS. The documentation in the download includes hardware and software requirements, example programs, and licensing information.

PX5 FILE is the first deeply embedded file system presenting a native Linux file system API to be certified by SGS-TUV Saar to the highest levels of the IEC 61508, IEC 62304, ISO 26262, and EN 50128 functional safety standards; offering developers a faster path to certification, reduced product liability with improved quality and accelerated time to market.

The MISRA compliance analysis was done using IAR’s advanced C-STAT static analysis tool. PX5 RTOS meets 292 out of the 297 rules and directives in MISRA C: 2012, making it one of the most compliant RTOS in the industry. The following are the only rules and directives not met by PX5 RTOS:

Please Contact Us for The Complete MISRA Compliance Report

| MISRAC2012-Dir-4.6_a | Basic types are used (low severity) |

| MISRAC2012-Dir-4.6_b | Typedefs of basic types without size or signedness (low) |

| MISRAC2012-Dir-4.9 | Function-like macros were detected |

| MISRAC2012-Rule-5.2_c89 | Identifiers not unique in first 31 characters (low severity) |

| MISRAC2012-Rule-5.4_c89 | Macro names not unique in first 31 characters (low) |

Complete OS-awareness is now available in Lauterbach’s TRACE32 debug solutions. Developers can debug the whole software stack from user application to device driver and in doing so, query and display all OS objects such as threads, message queues, event flags, semaphores, mutexes, memory pools, and timers. Trace32 PowerView software also provides dynamic views of PX5 RTOS scheduling analysis and symbolic function call trace and detailed performance analysis functions.

In a world of disagreement, virtually all experienced software developers would agree that there can never be enough software testing! We have all experienced the feeling that the latest software release is defect-free, only to be confronted with yet another issue. Please read Bill Lamie’s personal story on how an ounce of prevention is worth a pound of cure!

PX5 RTOS, PX5 FILE, and PX5 NET now support the Cortex-R52 processors of NXP’s advanced S32N55 processor platform. This support is integrated with the GrayVIP platform and can be evaluated on the S32N55-RDB evaluation board using the Lauterbach debugger, which also provides complete PX5 RTOS awareness.

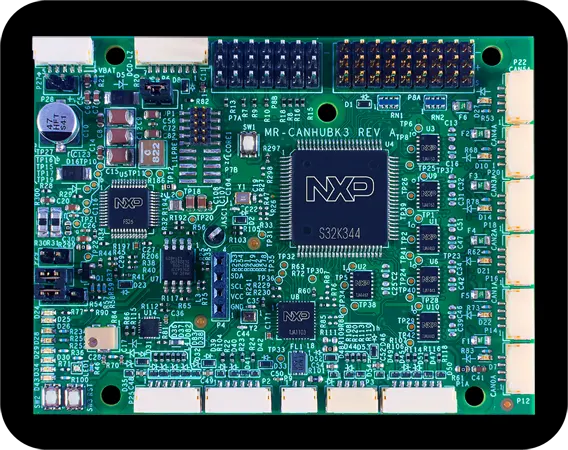

A free evaluation of PX5 RTOS for the MR-CANHUBK344 (Cortex-M7) is available for download on our website. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS specific extensions. This evaluation is based on S32 Design Studio development tools using the S32 Debug Probe (other debug probes may be used).

A free evaluation of PX5 RTOS for the S32K3X8EVB-Q289 (Cortex-M7) is available for download on our website. This evaluation contains 11 POSIX pthread examples (projects), including PX5 RTOS specific extensions. This evaluation is based on S32 Design Studio development tools using the on-board JTAG debugger (other debug probes may be used).

PX5 is actively pursuing functional safety certification for PX5 NET - the advanced TCP/IP networking stack.

New free evaluations for the following boards:

The PX5 RTOS is the fastest in the 2024 RTOS Performance Report issued by the Beningo Embedded Group. Based on the open-source ThreadMetric RTOS performance tests, the PX5 RTOS showed superior performance over three widely used RTOS. PX5 RTOS is the fastest RTOS Performance Report 2024

PX5 RTOS is event faster with IAR — roughly 30% faster!

The PX5 RTOS has achieved functional safety certification to the highest levels of the IEC 61508, IEC 62304, ISO 26262, and EN 50128 functional safety standards, specifically IEC 61508 SIL 4, IEC 62304 Class C, ISO 26262 ASIL D, and EN 50128 SW-SIL 4. Developers using the PX5 RTOS can leverage the RTOS certification artifacts to save time and money during application certification. For developers of both safety-critical and non-safety-critical devices, the certified PX5 RTOS offers a stable, reliable foundation built to industry best practices to support improved product reliability, security, quality, and time to market.

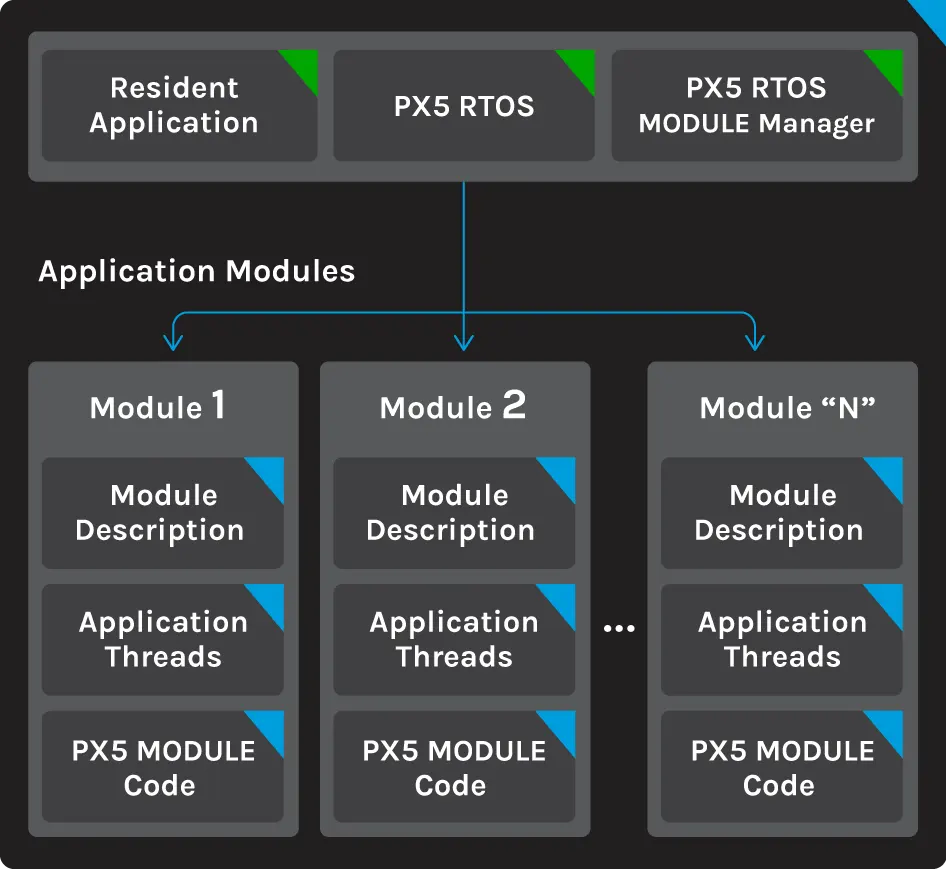

PX5 MODULES technology is analogous to a lightweight process or container, allowing developers to create and dynamically load/execute separately built application C programs called “Modules.” The “Module Manager” manages each Module and permanently resides with the PX5 RTOS and other application logic.

Each module has its own distinct instruction and data memory, which makes it possible to isolate its execution completely via MPU or MMU. Time-domain protection is also possible via maximum priority restriction on the threads running within the module.

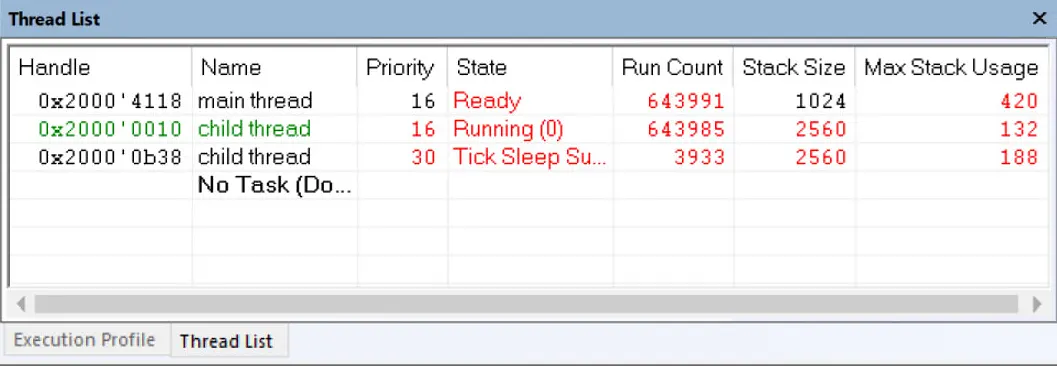

The PX5 RTOS C-SPY awareness plugin lets developers instantly visualize the state of RTOS-specific resources in their application. Visualization is available for all PX5 RTOS resources, including threads, condition variables, event flags, semaphores, mutexes, message queues, and memory pools. In addition, visualization of PX5 RTOS execution profiling information—when enabled by the developer—is available.

Visualization for all PX5 NET and PX5 FILE resources, including network interfaces, sockets, packet pools, volumes, and files, is also available. The PX5 RTOS C-SPY awareness plugin supports 32-bit and 64-bit architectures. It also supports all multicore configurations, including Asymmetric Multiprocessing (AMP) and Symmetric Multiprocessing (SMP). In SMP mode, the core associated with each running thread is clearly identified.

Please Contact Us for More Information

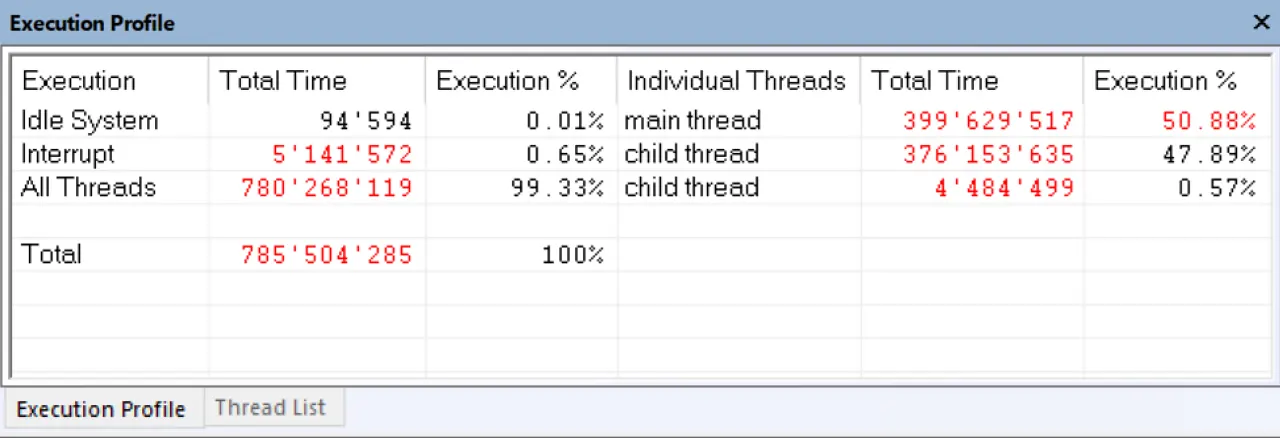

PX5 RTOS profiling tracks the total time the system is idle, executing threads, and processing ISRs. It also tracks the amount of time each thread is executed. This information helps developers better understand processor utilization and identify areas for optimization. This information can be obtained in the previously mentioned PX5 RTOS C-SPY plugin from IAR. Here is an example of the Execution Profile resource view of the pthread_create_example project:

This example shows very little idle time (0.01%), since threads run continuously. There is not much ISR processing either (< 1%) since the only interrupt processing is the periodic 1ms timer interrupt.

As for the threads themselves, the main thread and child thread are taking up most of the processing, while the priority child thread executes on every timer interrupt (< 1%).

Please Contact Us for More Information

The following are important links for PX5 Resources:

PX5 RTOS — px5rtos.com/px5-rtos-embedded

PX5 NET — px5rtos.com/px5-net

PX5 FILE — px5rtos.com/px5-file

PX5 MODULES — px5rtos.com/px5-modules

PX5 Videos — youtube.com/@px5rtos

PX5 White Papers — px5rtos.com/px5-rtos-white-papers

Ask me about PX5 RTOS—its industrial-grade design, technical advantages, and why it’s trusted by embedded developers. 🚀